|

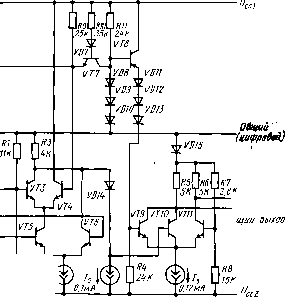

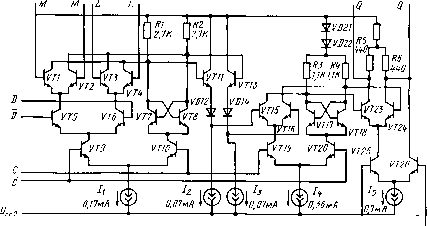

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) ( 13 ) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (13) Прямой Вход MfiSepmupyw ~ щий вход VDZ 37 VJJJ-\Z VII5II m 3j  \ 0,1mA -Прямой выход -Инвертирую- Рис 3 17 Схема преобразователей входных уровней ЦАП КМ1118ПА2, KPI 118ПА2 К£)6. При этом транзистор К/6 открыт и ток / подается на резистор RZ. Напряжение -0,8 В, создаваемое на резисторе Ri токами /1 и /2, смещается на диоде KD14 до -1,4 В и поступает на базу транзистора К/10. На базу транзистора V/11 от делителя напряжения R1, RS поступает напряжение -1,2 В. При этом 17 10 закрыт и выходные напряжения ПУ определяют состояние переключателя тока, построенного на транзисторах 1/79 и 17 11. При подаче на прямой вход ПУ низкого уровня ТТЛ 0,4 В транзистор VI7 открыт. На базу транзистора VI8 приложенное напряжение 0,6 В (сумма напряжения коллектор - эмиттер насыщенного транзистора Vl7 и низкого входного уровня) смещается эмиттерным повторителем на транзисторе I 8 и диодами VDW - VD\3 до -1,8 В и подается на базу транзистора 179. Ток /3 через транзистор К/11 подается на резистор R6 и создает на прямом выходе ПУ напряжение низкого уровня -1,2 В. На инвертированный вход ПУ через резистор Rb поступает падающее на диоде VD\5 напряжение -0,6 В, образующее высокий уровень. При подаче на вход ПУ высокого уровня ТТЛ (2,4 В) транзистор Vil работает в инверсном активном режиме. На базу транзистора VI8 поступает напряжение 2,8 В, падающее на диодах KD8- KD10, которое после смещения повторителем на транзисторе К78 и диодами KD11 - KD13 до -0,6 В подается на базу транзистора 1/79. При этом транзистор VT9 открывается, ток /3 поступает на резистор R5 и выходные уровни составляют -0,6 и -1,2 В на прямом и инвертированном выходах ПУ соответственно. При работе от уровней ЭСЛ (вывод 9 ИС соединяется с общим выводом цифрового сигнала) (см. рис. 3.16) напряжение Ucc\=0. Транзистор VT9 закрыт (см. рис. 3.17), так как напряжение, подаваемое на его базу (- 3,7 В), ниже напряжения на базе транзистора VTW (- 1,2 В). Выходные напряжения ПУ определяют состояние переключателя тока, построенного на транзисторах VTli) и VI \\. В этом режиме ток, протекающий через резистор R\2, меньше тока через резистор R\3. Транзистор VI 1 работает в режиме насыщения, напряжение на его коллекторе составляет около 0,2 В. Транзистор VT6 закрыт и ток /1 через транзистор VT5 подается на переключатель тока на транзисторах VT3 и VT4, который управляется входным сигналом. При отсутствии входного сигнала на инвертированном входе ПУ на базу транзистора VI3 от делителя HI, поступает пороговое напряжение -1,3 В. Высокий логический уровень (-0,81 В) на прямом входе ПУ (база транзистора V7"4) открывает транзистор VIA, и на резистор Ri поступает ток h, который создает на нем падение напряжения 0,4 В Это напряжение через диод VD\4 поступает на базу транзистора VT\0 и открывает его. На прямой выход ПУ поступает напряжение -0,6 В, падающее на диоде VD\5, на инвертированный выход поступает напряжение -1,2 В, падающее на диоде VD\5 и резисторе /5. При подаче на прямой вход ПУ низкого уровня ( - 1,85 В) открыты транзисторы VT3 и VT\ 1 и напряжения на прямом и инвертированном выходах ПУ соответствуют низкому и высокому выходным уровням соответственно. В парафазном режиме ЭСЛ принцип действия ПУ аналогичен. В этом режиме повышается помехоустойчивость схемы и уменьшается время задержки распространения сигнала. Преобразователи уровней остальных входов (входы Н, L, 2С, С, G) построены по аналогичным схемам. Входной регистр построен на двухтактных триггерах. Принципиальная схема григгеров 3-10-го разрядов приведена на рис. 3.18. Регистр состоит из входного логического устройства, построенного на транзисторах VT\ - 1/Г6, первого триггера на VT7, УТЬ, второго триггера на VT\b- 1/Г18. и стробируемого буферного каскада на транзисторах 1/723-К/26 Выходные уровни первого триггера согласованы с входными уровнями второго триггера с помощью эмиттерных повторителей на транзисторах VT\ - 1/Г13 Работа триггеров синхронизируется переключателем тока на транзисторах VT9, VT\Q и VT\9, VT20, управляемых синхронизирующим сигналом С. При подаче на вход С низкого уровня открыты транзисторы VT9 и УГ20 Ток / через транзистор VI9 поступает на переключатель тока на транзисторах VT5, VT6, управляемый входным сигналом разряда. Если на входы И и L поданы низкие уровни, открыты транзисторы VT2 и VT4 и на (цифровой)  Рис. 3.18. Схема триггеров регистров ЦАП КМт8ПА2, КР1118ПА2 вы.ход первого триггера подается сигнал, соответствующий состоянию входа D, так как триггер работает в режиме прямого входного кода. При подаче на вход Н высокого уровня открывается транзистор VT\. Если теперь на вход D поступает низкий логический уровень, то ток / течет не через резистор R2, как в режиме прямого входного кода, а через резистор R.\ п на выходах триггера появляются напряжения высокого уровня. В этом режиме напряжение на выходе триггера не зависит от состояния входа D и на выходе ЦАП устанавливается напряжение конечной точки ХП. Аналогичным образом при подаче на вход L высокого уровня, напряжения на выходах триггера всегда соответствуют низкому входному уровню независимо от состояния входа Z), а на выходе ЦАП в этом режиме устанавливается напряжение начальной точки ХП. Если высокий уровень подается на входы И ч L одновременно, сигнал, подаваемый на вход D, инвертируется и ЦАП работает в обратном коде. Если на вход С подан низкий уровень, первый триггер открыт и уровни на его выходе соответствуют входным уровням. Однако в этом режиме второй триггер закрыт и в нем хранится информация, соответствующая коду, который был подан на в\оды триггера в предыдущем такте. Во время изменения уровня с низкого на высокий на входах С открываются транзисторы VT\0, VJ\9, открывается вход первого триггера, а информация на его выходе запоминается транзисторами VT7, VT8. Одновременно открывается второй триггер и информация с выхода первого триггера поступает в буферный каскад. Если на входе G существует высокий уровень, ток /5 через транзистор VT25 подается на переключатель тока на транзисторах VT23, VT24 и напряжения на выходах Q регистра (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) ( 13 ) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) |

|

|