|

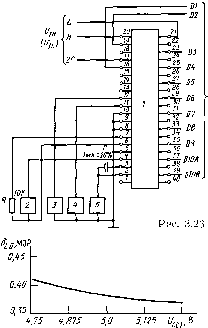

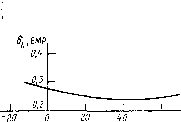

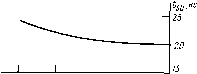

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) ( 15 ) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (15) г да \i4lL Рис. 3.21 I -J я - .20 77 II да m ш тл i да шов те шов Рис. 3.22  Рис. 3.24. Зависимость дифференциальной нелинейности ИС КМ1118ПА2, КР1118ПА2 от напряжения питания t/„i при t;„2=-5 В Рис. 3.21. Включение микросхем КМ1118ПА2, КР1118ПА2 при работе в режиме ТТЛ: / - ИС; 2 ~ источник опорного напряжения, 3 - генератор тактовых импульсов. 4 - генератор стробирующих импульсов; 5-источник питания Vc€\ , 6- источник питания Ucci Рис. 3.22. Включение ИС КМ1118ПА2, КР1И8ПА2 при работе в парафазном режиме ЭСЛ: / - ИС, 2 - источник опорного напряжения REF генератор тактовых импульсов; 4 - генератор стробирующих импульсов, 5 - источник питания Ucc2 Рис. 3.23. Включение ИС КМ1118ПА2, КР1118ПА2 при работе в режиме ЭСЛ: / - ИС, 2-источник опорного напряжения REF генератор тактовых импульсов; 4 - генератор стробирующих импульсов; 5-источник питания о,г5 - 0,21 - 0 2i %75 875 5,0 5,125 ЩсВ Рис. 3.25. Зависимость нелинейности ИС КМ1118ПА2, КР1118ПА2 от напряжения питания lJcc\ при Vcei- -5 в B37D - 20 - 15 -5,125 -5,0 -1,875 -1,75 Рис. 3.26. Зависимость дифференциальной нелинейности ИС КМ1118ПА2, ltP1118nA2 от напряжения питания Ucc2  во т,% Рис. 3.28. Зависи.мость нелинейности ИС КМ1118ПА2, КР1118ПА2 от температуры - 0,245 - 0,240 0,235 l/cc2>B ,0 -4,875 -4,75 Рис. 3.27. Зависимость нелинейности ИС KMl 118ПА2, KPl 1 18ПА2 от напряжения питания Uca O.S - "дТг--- I 0,2 60 J," С Рис. 3.29. Зависимость дифференциальной нелинейности ИС КМ1118ПА2, КРИ18ПА2 от температуры -5,125 -5,0 -¥,875 -4,75 Si. в,МЗР z 0,38 - 0,31 0,36 Рис. 3.30. Зависимость напряжения смещения нуля ИС КМ1118ПА2, КР1118ПА2 при включении от напряжения питания Ucci в режиме ЭСЛ  ИсгВ -5,125 -5,0 -f,S75 -t,75 Рис. 3.31. Зависимость погрешности ИС КМ1118ПА2, КР1118ПА2 в конечной точке ХП от напряжения питания Ucc2 в режиме ЭСЛ

60 T,°C 60 T,°C Рис. 3.32. Зависи.мость времени установления при включении от температуры в режиме ЭСЛ Рис. 3.33. Зависимость времени установления при выключении от температуры в режиме ЭСЛ старший разряд младший разрлд тттттттт т-хл: /4м буф \ZR \2.R 2Д l2/f Рис 3 34 Структурная схема ЦАП К1118ПА1, КМ1118ПА1 В данном ЦАП применена структура с комбинированным способом формирования разрядных токов, в которой токи пяти старших разрядов формируются с помопхью ИТ со взвешенными резисторами, а трех младших - с помощью ИТ с матрицей R-2R. Для сокращения общего числа эмиттерных переходов в ИТ транзисторы трех младших разрядов работают при плотности тока через переход, уменьшенной в 4 раза по отношению к старшим разрядам [32]. В четырех старших разрядах разрядные токи формируются с помощью параллельно включенных одинаковых ИТ, число которых в каждом разряде соответствует весу разряда. Разрядный ток старшего (первого) разряда формируется восемью параллельно включенными ИТ на двухэмиттерных транзисторах, а последующих три разряда содержат 4,2 и 1 ИТ соответственно. Транзистор ИТ пятого разряда содержит только один эмиттер (по сравнению с двумя в четвергом разряде). Такое решение позволяет исключить влияние геометрии транзисторов ИТ на нелинейность характеристики преобразования. В отношении числа эмиттерных переходов такая структура эквивалентна обычной структуре со взвешенными резисторами. В ИТ трех младших разрядов использованы транзисторы, геометрические размеры которых равны размерам транзисторов старших разрядов, но работающие при плотности тока эмиттерных переходов в 4 раза меньшей. Так как потенциалы эмиттеров всех ИТ равны, то напряжение транзисторов ИТ трех младших разрядов должно отличаться от предыдущих на величину A\Jъ(, = 11x1 h, где фт- - температурный потенциал. Эта разность напряжений создается током /см на резисторе /?см, включенном в общую базовую шину между транзисторами ИТ пятого и шестого разрядов. Значение сопротивления /?см выбирается с учетом базового тока транзисторов младших разрядов и его разброса. Резисторная матрица для (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) ( 15 ) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) |

|

|