|

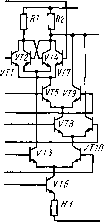

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) ( 21 ) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (21) для преобразования унитарного (термометрического) кода на выходе компараторов в позиционный код. Для этого входы схемы И на выходе любого компаратора (кроме КО и /(63) соединены с выходами еще двух соседних компараторов. При срабатывании ряда компараторов от входного аналогового сигнала высокий уровень напряжения будет на выходе схемы И последнего сработавшего компаратора. Другие схемы И, как сработавших, так и еще не сработавших компараторов, будут иметь низкий уровень напряжения на своих выходах. Это происходит потому, что выходной сигнал п-\- 1 компаратора на схему И л-го компаратора подается в противофазе с выходными сигналами, подаваемыми на ту же схему И (л-1)-го и л-го компараторов. Такая обработка выходного кода компараторов исключает неопределенность, тем самым повышается помехоустойчивость АЦП. Электрическая принципиальная схема одного элемента И первой ступени шифратора приведена на рис. 4.3. Выполнена она на основе дифференциальных переключателей тока. Особенностью является наличие парафазных входов, что позволило обойтись без дополнительных источников опорных напряжений и повысить быстродействие и помехоустойчивость шифратора. В состав схемы И входит триггер-защелка, выполненный на транзисторах V72 и VT4. На транзисторах VT3 и VTIO построен переключатель режима работы схемы И. При подаче высокого уровня на инверсный тактовый вход и низкого уровня на прямой тактовый вход элемент И выполняет свои логические функции. При обратной подаче уровней на тактовые входы схемы И ток ИТ, построенного на транзисторе VT6, запитывает триггер-защелку, и на выходе схемы И запоминается результат сравнения. Схемы И и компараторы тактируются в противофазе, поэтому, когда компараторы работают в режиме сравнения и выдают на выходе результаты сравнения напряжений, шифратор на своем выходе сохраняет код прежней выборки. При запоминании компараторами нового значения выборки шифратор производит ее шифрацию в позиционный код. Результат первой шифрации снимается с резисторов R2 схем И. Вторая ступень шифратора состоит из двух шифраторов позиционного кода в двоичный код. Первый шифратор преобразует позиционный код с выходов первых 32 схем И в 5-разрядный двоичный код, соответствующий нижней половине динамического диапазона. Второй шифратор преобразует позиционный код с выходов оставшихся 32 схем И в 5-разрядный двоичный код, соответствующий верхней половине динамического диапазона, и формирует начало 6-го разряда. Оба шифратора построены на основе элементов ИЛИ. Принципиальная схема части шифратора одного разряда приведена на рис. 4.4. Элемент ИЛИ выполнен на основе дифференциального пере- момпараФара п Вых. 1 дрямай номпарптора п Вых 2. прямой иомпйратора п-1 Вых zuftffepciwu MOMrtaротора п-1 Bdix S амверстш HOMhapamopa n+f Вы)!,3 лрлмай NOMnapamapa п+1 Выход тактовый прямой „ ВьЬаВ тая та Вый ф9ерсяь/й mixaff йпармга яа-Нрлнемил  Общий („аналоговая земля) вд/ход VT11 1 II VT(N*l) Н базам транзисторов других разрядоб Н базам транзисто--ров других разрядов -Выход I- Общий („аналоговая" земля) VB1 R5 Рис 4 3 Принципиальная электрическая Рис 4 4 Принципиальная электри-схема элемента И первой ступени шифратора ческая схема части шифратора вто-АЦП К1107ПВ1 рой ступени одного разряда АЦП К1107ПВ1 ключателя тока. Правйе (ho схеме) плечо переключателя тока собрайо на .транзисторе Vl"2. Левое образуется линейкой транзисторов» базы которых подключаются к выходам схем И первой ступени шифратора. Йри появлении высокого уровня на выходе какой-либо схемы И Соответствующие транзисторы линейки включаются, и на выходах схем ИЛИ формируются высокие логические уровни. По Построению оба шифратора одинаковы. Схема одного из них приведена на рис. 4.5. Нумерация горизонтальных лийий обозначает номер выходов схем И шифратора первой ступени. Э+и входы шифратора и представляют собой соединенные базы т)анзисторов левого плеча схем ИЛИ. Число параллельно включенных транзисторов на каждом входе определяется числом точек на пересечении горизонтальных и вертикальных линий. Кроме того, эта точка означает подсоединение эмиттера соответствующего транзистора к данной разрядной шине, которые обозначены вертикальными линиями. Первый шифратор формирует 5-разрядный двоичный код, причем выход, образованный «нулевой» схемой И, в дальнейшем не используется. Второй шифратор формирует также 5-разрядный двоичный код кроме него - начало шестого разряда, обозначенного Q1. Такое построение шифратора позволило повысить его быстродействие по сравнению с шифратором, который формировал бы сразу Полный 6-разрядный двоичный код за счет уменьшения числа эмиттеров транзисторов, подключенных к разрядной шине. 3* 67 2-3- 5-6-7-в-9 -Ю- 11-12-13- Вх 1 опорного напряжения Вход регистра - Общий („аналогодам" -Выход Вход тантоВб/й прямой вход тонтовет инвераныи Вх. Z апориога напряжения J VTZ \УТ6 lccZ- Qiq2Q3om(i6(M3p) Рис. 4.5. Шифратор второй ступени АЦП К1107ПВ1 Рис. 4 6 Принципиальная электрическая схема регистра хранения одного разряда Увеличение числа эмиттеров приводит к увеличению емкости на выходе разрядной шины, что, в свою очередь, приводит к росту задержки /" шифратора. Повышение рабочего тока элемента ИЛИ не представляется возможным ввиду ограничения допустимой плотности тока через эмиттер рабочего транзистора. Увеличение периметра эмиттера с целью увеличения допустимого тока через него приводит к росту размеров транзистора и, как следствие, к увеличению паразитных емкостей, ввиду чего увеличение быстродействия шифратора делается незначительным. Сформированный код с выходов элементов ИЛИ поступает на вход промежуточных регистров хранения. Принципиальная электрическая схема промежуточного регистра хранения для одного разряда изображена на рис. 4.6. Этот регистр необходим для хранения двоичных кодов, полученных в результате второй шифрации. В состав регистра входит переключатель режима работы, выполненный на транзисторах V12 и КГ6, переключатель тока на транзисторах У71 и К77, триггер-защелка на транзисторах К73 и Vlb. На вход регистра подается код, сформированный на выходах схем ИЛИ второй ступени шифратора, на второе плечо переключателя тока - опорное напряжение, равное середине перепада входного сигнала. Регистр тактируется в противофазе (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) ( 21 ) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) |

|

|