|

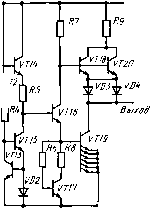

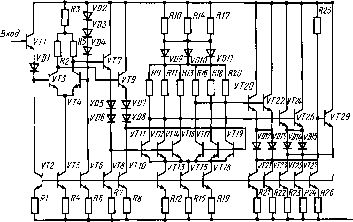

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) ( 22 ) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (22) с элементами И. При подаче на инверсный тактовый вход высокого, а на прямой - низкого уровня регистр работает в режиме приема информации, и информация, поступающая на его вход, проходит без инвертирования на его выход. При подаче обратного тактового сигнала срабатывает триггер-защелка, и информация на выходе регистра запоминается. Третья ступень щифрации предназначена для объединения двух 5-разрядных двоичных кодов с выходов регистров в полный 6-разрядный двоичный код. Шифратор построен на элементах ИЛИ, схемотехнически полностью соответствующих аналогичным схемам второй ступени шифратора. Схема шифратора третьей ступени изображена на рис. 4.7. Здесь вертикальными линиями обозначены входы шифратора, которые являются базами транзисторов. На первых (слева) пяти входах стоит по одному транзистору. На вторых шести входах - по два. Точками обозначено подключение эмиттеров транзисторов к соответствующим разрядным шинам, которые показаны горизонтальными линиями. Каждая разрядная шина является левым плечом дифференциального переключателя тока элемента ИЛИ, аналогично изображенному на рис. 4.5. На выходах схем ИЛИ получается сформированный 6-разрядный двоичный код. С выходов схем ИЛИ третьей ступени шифратора сформированный двоичный 6-разрядный код подается на входы схем ИСКЛЮЧАЮЩЕЕ ИЛИ, которые служат для выбора типа выходного кода. Принципиальная электрическая схема ИСКЛЮЧАЮЩЕЕ ИЛИ, выходного буферного регистра и преобразователя внутрисхемных уровней в выходные уровни ТТЛ представлена на рис. 4.8. Схема ИСКЛЮЧАЮЩЕЕ ИЛИ выполнена на дифференциальных переключателях тока на транзисторах VT2, К76, VT\, VTA, VTIO, VTW. Нагрузкой схемы служат резисторы R\ и RZ, образующие парафазный выход. На выход управления кодом подается управляющий сигнал, изменением которого можно инвертировать сигнал на парафазных выходах схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. Выходной регистр хранения выполнен на основе триггера-защелки, управляемого переключателем тока. При подаче на прямой тактовый вход высокого уровня, а на инверсный - низкого включается схема BxodbJ 010гдзв4в5 ai QZQ3QtQ5Q6 Рис. 4.7. Шифратор третьей ступени АЦП К1107ПВ1 -QUC3P) -Q2 -аб(МЗР) Вход у продления ходом Вход опорного напртения VonJ-Вход инутрма- liUOfiHtilU. Вход опорного напряжения Lfq f" Вход /пантовый прямой Вход тантовйш индерстй Вход опорного напряжения - • VD1 ЛУупХт/ЛАтвЛ-Л 1 у* VTZ JvTJ  Urr1 = S& Одщий с, цифраваяэемля) VT7 1 Рис. 4.8. Схема ИСКЛЮЧАЮЩЕЕ ИЛИ, буферного регистра и выходного преобразователя уровня АЦП К1107ПВ1, КП07ПВ2 ИСКЛЮЧАЮЩЕЕ ИЛИ и формирует на своих выходах уровни, определяемые уровнем сигнала на информационном входе и на выходе управления кодом. При смене тактового сигнала включается триггер-защелка и фиксирует информацию на выходе схемы ИСКЛЮЧАЮЩЕЕ ИЛИ. Снимаемый с нее парафазный сигнал подается на преобразователь уровня, выполненный на транзисторах VT\2-VT20. Для увеличения выходного тока лог. О до 2 мА выходной транзистор Vi 19 сделан мйОгоэмиттерным. Преобразователь уровня служит для преобразования внутрисхемных низкоуровневых ЭСЛ перепадов 300...500 мВ Й ctanflapTHbie ТТЛ-уровни. Преобразователи уройня сигналов управления предназначены для преобразования входнкх ТТЛ-уровней, подаваемых на тактовый вход и входы управления типом выходного кода, в уровни, необходимые для нормальной работы схемы. Принципиальная электрическая схема особенностей не имеет, построена на основе ключа с общей базой и упрайляется по цепи эмиттера. Схемы синхронизации необходимы Для формирования тактового сигнала, поступающего с выхода входного преобразователя уровня тактового сигнала, в сигналы с уровнями, пригодными для управ- ления компараторами, схемами И, промежуточными регистрами и выходными регистрами хранения. Всего в состав АЦП входят пять схем синхронизации. Четыре из них предназачены для обслуживания компараторов, схем И, промежуточных регистров хранения и одна схема синхронизации - для выходных буферных регистров. Каждая из четырех схем синхронизации формирует тактовые сигналы для стробирования 16 компараторов, 16 схем И и 4-х разрядов промежуточного регистра хранения. Принципиальная электрическая схема одной из четырех схем синхронизации приведена на рис. 4.9. Схема представляет собой усилитель-формирователь, имеющий два каскада усиления, выполненных на основе дифференциальных усилителей на транзисторах VT3, VT4 и К7Т1-К719. На выходе схемы имеются два мощных эмиттерных повторителя, работающих на источники тока. Выход схемы парафазный. Принципиальная электрическая схема схемы синхронизации выходных буферных регистров подобна рассмотренной выше и отличается лишь способом организации режимов каскадов по постоянному току. Следует отметить конструктивную особенность построения системы синхронизации АЦП. Длина проводников, соединяющих выход схемы преобразователя уровня со входами схем синхронизации для обеспечения равенства задержек распространения сигналов по ним, конструктивно выполнена одинаковой, что позволило уменьшить разброс времен срабатывания компараторов по тактовым входам в различных линейках, т. е. уменьшить разброс апертурного времени по ХП.  Общий Срмалогодая"Земля) Выход иядерсяый УШ Выход /г/мм ой Рис. 4 9. Принципиальная электрическая схема синхронизации компараторов, элементов И и промежуточного регистра хранения (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) ( 22 ) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) |

|

|