|

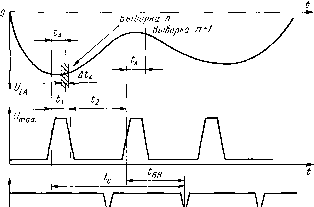

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) ( 23 ) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (23) Рассмотрим временную диаграмму работы АЦП К1107ПВ1 (рис. 4, 10) [37, 38]. С приходом тактового импульса на тактовый вход АЦП компараторы спустя время фронтом переводятся в режим хранения. Время является апертурным временем и равно сумме времен задержек входного преобразователя уровня, схемы синхронизации компараторов, времени разрешения триггеров-защелок и в зависимости от конкретной микросхемы и температуры окружающей среды составляет 10...22 не. Однако случайные изменения этого времени (апертурная неопределенность в конкретной точке ХП) крайне малы и равны примерно 30 пс. Этим же фронтом схемы И первой ступени шифратора переводятся в режим приема информации. За время длительности импульса t\ код с выходов компараторов должен быть преобразован шифратором первой ступени и появиться на выходах схем И. Срезом тактового импульса компараторы переводятся в режим сравнения, а схемы И шифратора первой ступени - в режим хранения информации кода выборки п. Кроме того, этот срез тактового импульса устанавливает промежуточные регистры в режим приема информации. За время паузы тактового сигнала /г код выборки п с выходов шифратора первой ступени должен пройти шифрацию второй ступенью шифратора и установиться на выходе промежуточного регистра хранения. С приходом второго тактового импульса компараторы фиксируют на своих выходах значение выборки п-\-\. Шифратор первой ступени вновь переводится в режим приема информации кода выборки д + 1, а выходной буферный регистр в режиме приема информации кода выборки п. За время длительности второ-  Нод выборки п.-2 Мов выоорки/!-fjJfoe вб/ворки/гМоввд/дорна Рис 4 10 Временная диаграмма работы АЦП К1107ПВ1 го тактового импульса код выборки должен пройти шифрацию третьей ступенью шифратора и установиться на триггере-защелке выходного буферного регистра. С приходом среза второго тактового импульса выходной буферный регистр фиксирует на своем выходе код выборки п, который спустя время задержки выходных преобразователей уровня появляется на выходах микросхемы. Время задержки от фронта тактового импульса до появления кода на выходах микросхемы называется временем задержки выходного буферного регистра которое не превышает 50 не. Таким образом, благодаря применению четырех стробируемых каскадов с хранением информации при времени преобразования 100 не удалось получить частоту преобразования 20 МГц, т. е. кодирование сигнала и изменение кода на выходе производятся каждые 50 не, в то время как код соответствующей выборки появляется на выходах АЦП через /,= 100 НС. Рассмотрим некоторые особенности применения ИС К1107ПВ1. 1. Выводы питания микросхемы должны быть зашунтированы параллельно соединенными конденсаторами типа К53-1 (К53-4) емкостью 10 мкФ и КМ5 (КМ6) емкостью 0,1 мкФ. 2. Допустимые амплитудные напряжения пульсаций питающих напряжений не должны превышать 60 мВ. 3. Допустимое значение статического потенциала 100 В. 4. Отклонение опорного напряжения Uief\ вызывает появление дополнительной погрешности, эквивалентной напряжению смещения нуля на входе АЦП, равной по величине отклонению опорного напряжения. 5. Отклонения опорного напряжения (J/ef2 вызывают появление дополнительной погрешности, эквивалентной абсолютной погрешности преобразования в конечной точке шкалы, равной по величине отклонению опорного напряжения. 6. При использовании вывода J2 «Корректировка нелинейности» необходимо учитывать, что любая нагрузка, подключаемая к средней точке делителя, оказывает влияние на нелинейность микросхемы. 7. Для уменьшения наводок, образуемых выходными ТТЛ-каскадами, необходимо предусмотреть отдельные шины «цифровая» земля и «аналоговая» земля с соединением их только в одной точке на зажиме источника питания. При этом разность потенциалов между выводами микросхемы «аналоговая» и «цифровая» земля не должна превышать 100 мВ. 8. Выходное сопротивление источника аналогового сигнала в диапазоне рабочих частот не должно превышать 25 Ом. При спектре входного сигнала более 6,5 МГц для получения гарантированной монотонности ХП на входе АЦП необходимо применять дополнительное УВХ. Практически ИС имеют запас по допустимой скорости изменения входного сигнала, при которой обеспечивается монотонность ХП; для ряда схем эта величина достигает значения 75 Б/мкс, что соответствует частоте синусоидального сигнала 12 МГц при амплитуде 1 В. Вопрос о применении УВХ на входе АЦП должен решаться в каждом индивидуальном случае, в зависимости от конкретной задачи. Основной критерий необходимости применения внешней схемы УВХ - монотонность ХП и динамическая линейность. Ориентировочно можно сказать, что среднее квадратическое значение нелинейности ХП ИС К1107ПВ1 при частоте входного синусоидального сигнала 2,5 МГц не превышает ±0,7 ЕМР. 9. Для выбора типа выходного кода на выводы 48 и 44 микросхемы могут подаваться как стандартные ТТЛ-уровни, так и потенциал «цифровая» земля, эквивалентный низкому логическому уровню, или напряжение источника Ucc\=5 В без дополнительных резисторов, эквивалентное высокому логическому уровню. Зависимость выходного кода микросхемы от комбинации уровней на управляющих входах приведена в табл. 4.1. Таблица 4.1. Зависимость выходного кода от комбинации уровней на входах управления для ИС К1107ПВ1

Примечание. Уровни на цифровых выходах соответствуют значению иапряжеиия на аналоговом входе микросхемы UiaO В. 10. При использовании АЦП с максимальной частотой преобразования 20 МГц рекомендуемая длительность импульса тактового сигнала 15 не, паузы 35 не. 11. При записи выходной информации АЦП во внешний регистр хранения или память момент записи должен соответствовать фронту тактового сигнала АЦП. 12. Емкость нагрузки цифровых выходов не должна превышать 30 пФ. 13. Выводы микросхемы, имеющие одноименное назначение (табл. 4.1), должны быть электрически соединены на печатной плате в непосредственной близости от корпуса микросхемы. 14. Возможный вариант принципиальной электрической схемы включения микросхемы К1107ПВ1 приведен на рис. 4.11. Схема формирует необходимые опорные напряжения и содержит входной буферный усилитель аналогового сигнала. (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) ( 23 ) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|