|

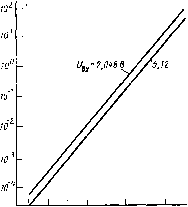

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) ( 65 ) (66) (67) (68) (69) (70) (71) (72) (73) (65) где f(QA, Qn Qe, Qc, Qp) - функция, зависящая от эксплуатационных характеристик схем; - временная стабильность; Qr - температурная стабильность; Qe - стабильность к воздействию окружающей среды; Qc - стабильность к изменениям питающих напряжений; Qp-потребляемая мощность; А - стоимость микросхемы. При проектировании АЦП с улучшенной добротностью возникают проблемы, связанные с изготовлением компонентов схемы с заданными характеристиками при их большом количестве на кристалле большой площади при приемлемом проценте выхода годных. Увеличение добротности АЦП и ЦАП в основном определяется повышением их быстродействия и разрядности при снижении стоимости. Одновременно увеличить разрядность и быстродействие очень сложно, так как эти требования взаимно противоречивы. Увеличение разрядности обусловливает увеличение числа составных единиц АЦП или числа циклов, за которое происходит преобразование, коэффициентов усиления устройств, работающих в линейном режиме, что, в свою очередь, приводит к снижению быстродействия. Увеличение разрядности АЦП параллельного типа связано с увеличением числа шагов квантования ХП. Увеличение числа шагов квантования приводит к уменьшению их величины. Увеличение диапазона входных напряжений АЦП свыше 5...6 В ограничивается пробивными напряжениями транзисторов, так как граничная частота усиление транзисторов в общем случае обратно пропорциональна пробивным напряжениям. С уменьшением величины шагов квантования резко возрастают требования к точности изготовления компонентов для получения необходимых нелинейности и дифференциальной нелинейности. Кроме того, с увеличением разрядности увеличивается «токовая» составляющая нелинейности (см. гл. 2) [114, 116, 117]. Отклонение опорного эталонного напряжения на /-м компараторе, обусловленное протеканием входных токов компараторов через резисторы делителя, определяется [112] как Д.(0 = 2 [/.Е. 2Ч(2--/>-,]/?---i 2 [Vf 24(2--/>,]/? = (2*--Oi, где MJjfii) - отклонение опорного напряжения на (-м компараторе; REt - ток через делитель; ig - входной ток компаратора; R - номинальное сопротивление резистора в делителе опорных напряжений. Максимальное отклонение будет в середине ХП при / = 0,5-2: At/;?max=(/fi/?/2) (2-0,5-2)-0,5-2 = /g/?22/8. При изготовлении резисторов делителя в слое металлизации ИС из сплава AL - Si ввиду особенностей конструкции топологии минимально возможным.следует считать сопротивление /? = 0,16 Ом. При приемлемой входной полосе частот компаратора его входной ток (gil мкА. На рис. 9.1 представлена зависимость «токовой» составляющей нелинейности для АЦП разной разрядности и с разным диапазоном входного сигнала. Как видно из графика, возникающая погрешность обратно пропорциональна диапазону входного сигнала АЦП и экспоненциально возрастает с увеличением разрядности. Рис. 9.1. Зависимость «токовой» составляющей нелинейности от числа разрядов АЦП при 7? =0,16 Ом, 1в= 1 мкА  If 5 В 18 9 10 Ь, Sam Если для 68 этой составляющей можно пренебречь, то при дальнейшем увеличении разрядности она является преобладающей. Разброс сопротивлений резисторов делителя также определяет нелинейность ХП АЦП. Сопротивление резистора зависит от толщины резистивного слоя, его ширины, длины и удельного сопротивления материала, из которого он изготовлен. Исследования показывают, что флуктуациями планарных геометрических размеров и удельного сопротивления материала можно в первом приближении пренебречь, и значение сопротивления резисторов определяется в основном толщиной слоя резистивного материала [ИЗ]. Распределение толщины слоя не является случайным, обычно его толщина постепенно изменяется в одном направлении. Считая, что вдоль вертикального направления толщина слоя увеличивается на а% (сверху вниз), а вдоль горизонтального на 6 % (слева направо), в [П2] получены формулы для расчета возникающей погрешности для 8-разрядного АЦП. В анализируемой конструкции АЦП компараторы размещены четырьмя блоками. В каждый блок входит по две линейки из 32 компараторов. Такая компоновка является оптимальной и поэтому традиционной при разработке топологии параллельных АЦП. Максимальное значение возникающей погрешности [ЕМР] вдоль горизонтальной стороны Кристалла (поперек линеек компараторов) составляет Emai =32/100. Максимальное значение возникающей погрешности [ЕМР] вдоль вертикальной стороны кристалла (вдоль линеек компараторов) составляет 8тах2 = 4а/100. Таким образом, максимальная погрешность, вызываемая неоднородностью толщины слоя резистивного материала делителя, прямо пропорциональна числу компараторов в линейке. В табл. 9.1 приведены значения допустимой относительной погрешности толщины Таблица 9.1. Требования к неоднородности толщины слоя резистивного материала

слоя резистивного материала делителя в горизонтальном направлении (поперек линеек компараторов) в зависимости от числа разрядов при допускаемой возникающей погрешности 0,5 ЕМР. Еще одним фактором, влияющим на нелинейность ХП АЦП, является разброс значений напряжения смещения компараторов. Напряжение смещения определяется в основном разностью напряжений Л/бэ транзисторных пар А/бэ=Ярз£, 21, Rc, h, S). Допустимые отклонения указанных параметров для достижения заданной нелинейности, равной ±0,5 МЗР, рассчитанные на условия наихудшего их сочетания, приведены в табл. 9.2. Таблица 9.2. Допустимые отклонения параметров, влияющих на At/g

Примечания. 1. Расчет параметров табл. 9.2 произведен иа основании конкретных приицнпнальиых схем компараторов. 2. Расчет произведен исходя из следующего распределения составляющих: иа долю разброса площадей эмиттеров приходится ОЛ ЕМР; на долю разброса контактных сопро-тивлеиий к эмиттеру 0,05 ЕМР; на долю разброса поверхностного сопротивления слоя эмиттера 0,05 ЕМР; иа долю разброса статического коэффициента усиления транзисторов 0,1 ЕМР; на долю погрешности, вносимой делителем опорных напряжений, 0.1 ЕМР; иа долю погрешности, вносимой коллекторными резисторами нагрузки компараторов, 0,1 ЕМР. (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) ( 65 ) (66) (67) (68) (69) (70) (71) (72) (73) |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|