|

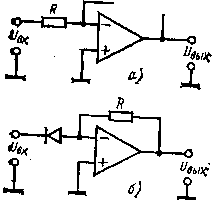

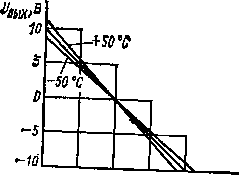

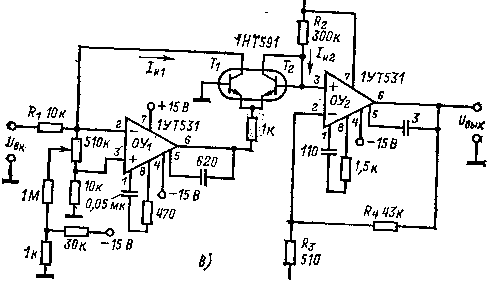

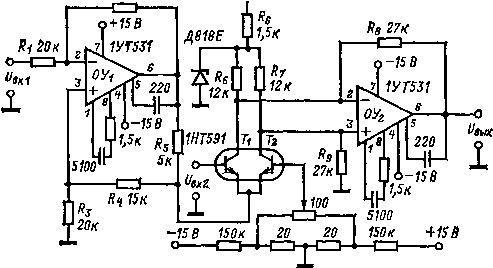

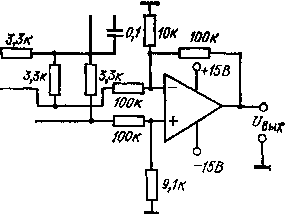

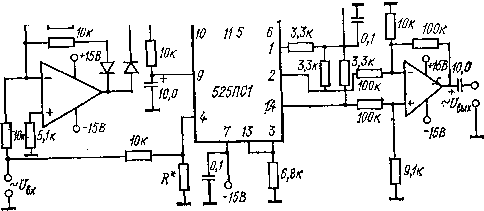

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) ( 12 ) (13) (14) (15) (16) (17) (18) (19) (20) (12) можно компенодровать с помощью термореаистора в цепи ОС, который должен иметь TKR~0,%/°C. Температурную чувствительность постоянной составляющей компенсируют путем включения дополнительного диода, через который пропускают неизменный ток: Если характеристики диодов согласованы, то член In/о исключается. Рассмотрим схему логарифмического усилителя на рис. 54, в [23,   C,OOS 0,05 0,5  Шт Рис. 54. Логарифмический (о) и антилогарифмический (б) усилители, практическая схема логарифмического усилителя (в) его выходная характеристика (г). 40]. Она содержит инвертирующий ОУ1, в цепь ОС которого включен транзистор Ти Путем введения согласованного транзистора Га компенсируется член In /0. Усилитель ОУа включен как неинвертирующий буферный усилитель. Для операции логарифмирования используется не абсолютное падение напряжения на р-п-переходе, а приращение напряжения на 72 перепаде база - эмиттер согласованной пары транзисторов. При увеличении дифференциального тока: К2 - 0 (54) f6i,62 = Фт In (/ki/ks)- Ток /в1 является входным током ОУ1, поэтому /к1 = /вх ?1. Ток /к2 определяется положительным напряжением питания и резистором /?2: Тогда напряжение Между базой и эмиттером Af/ea = Фт Ш (f/вх R2IRin). (55) Так как база транзистора Ti заземлена, приращение Дбэ дается на вход ОУа, имеющего коэффициент передачи (/?4/а)Н-1. Таким образом, i/вых = Фт [(/?4 ?з) + 1 ] In (С/вх RJRiUn)* (56) В десятичных логарифмах f/вых = 2,3фт [{RJRs) + 1] lg (t/вх RJRiUn) (57) Наклон логарифмической характеристики определяется сопротивлением резистора /?4, а точка пересечения нуля - сопротивлением резистора Rz. Температурная нестабильность выходной характеристики на рис, 54, г составляет примерно 0,3 %/°С, Для ее компенсации следует последовательно с резистором /?з включить соответствующее термосопротивление. 31. Аналоговое умножение и деление Множительные устройства находят широкое применение в узлах электронной аппаратуры. Основные методы выполнения операции умножения: логарифмический, разности квадратов, усреднения прямоугольного напряжения, время-импульсный, нормировки токов и переменной крутизны. Описание указанных методов содержится в [1,10,49]. Метод переменной крутизны отличается схемной простотой, но требует наличия согласованных по характеристикам пар биполярных или полевых транзисторов. Элементом умножения схемы на рис. 55 [23] является транзисторная пара Ti-Тг. Коллекторный ток транзистора Ti (58) 73 продифференцировав h по Ucau найдем: dhIdU6i = IJT- (59) Если дифференциальное входное напряжение равно нулю, те ток /, подаваемый на эмиттеры, равномерно распределяется между двумя транзисторами, т. е. 11=1/2. R2 20k о+Г55  Рис. 55. Умножитель на согласованной паре биполярных транзисторов. Усилитель ОУ1 представляет собой преобразователь входного напряжения f/exi в ток /. Если выполнить соотношение Ri{Ri.-\-Rb)=RiRi, то / = RJUbxi/RbRi (60) приращение дифференциального тока dlidl,= ~--ridUQ,i-dUQ,,). (61) Фт 2 С учетом того, что tBx2=rft/Q3j-rfl/jg, Ri-Rb найдем вы ходное напряжение Свых = ад1/вх11/вх2/2фтад1. (62) Нужно отметить, что пары резисторов Re-Rj и Rs-R» должны быть подобраны с точностью 0,1 %. Уравнение (62) справедливо для малого сигнала, поэтому Ubxz должно быть не более ±20 мВ, что обеспечивает удовлетворительную линейность. Напряжение Uaxi может быть только положительным. Наилучшей совокупностью параметров обладают интегральные умножители с нормировкой (отношением) токов [37]. Схема умножителя типа 525ПС1 представляет собой счетверенный дифференциальный усилитель с перекрестными коллекторными связями. Путем логарифмирования и антилогарифмирования одного из входных сигналов с последующим умножением его на другой входной сигнал обеспечивается выходное напряжение, пропорциональное произведению двух сигналов с учетом алгебраического знака (четырехквадрантное умножение). На рис. 56 изображена схема включения умножителя. На выводы 9 и 4 подаются сигналы Ux и Uy. Коэффициент передачи по

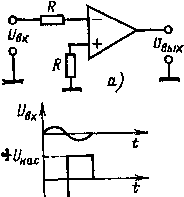

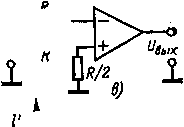

ВоАансироВка ггг нуля  Рис, 56. Аналоговый умножитель на основе микросхемы 525ПС1 с нормировкой токов. 8,2к 8,2к  Рис. 57. Схема квадратора для сигналов переменного напряжения. каждому каналу можно регулировать резисторами Rx и Ry. Резисторы Ri и Rz определяют эмиттерные токи дифференциальных каскадов и общий коэффициент передачи. На схеме указаны номиналы резисторов для входных сигналов, изменяющихся в диапазоне rfclO В,. общего коэффициента передачи, имеющего значение около 0,1, что обеспечивает выходное напряжение в пределах ±10 В. Можно объединить выводы 3 и 13, включив резистор с сопротивлением 6,8 кОм. Выводы 8 ч 12 предназначены для балансировки нуля по каждому каналу. Точность перемножения составляет 2- 5 % в диапазоне температур ±60 "С. Операционный усилитель, включенный на выходе умножителя, преобразует дифференциальный токовый сигнал в выходное напряжение UsbLX = f<lUxUy-, (63) где Ki - коэффициент пропорциональности. Умножитель можно использо- 1вх2 Щых /Умножч- Рис. 58. Метод аналогового деления с использованием умножителя. вать для возведения сигнала в квадрат, извлечения квадратного корня, вычисления тригонометрических функций, удвоения частоты, модуляции и т. д. На рис. 57 изображена схема, имеющая квадратичную зависимость между входным и выходным синусоидальными напряжениями. Входной сигнал подается на один из входов умножителя через резисторный делитель, на другой вход сигнал подается после прецизионного выпрямления и сглаживания. Любой умножитель можно превратить в делитель, если использовать схему, изображенную на рис. 58. На один из входов умножителя подается выходное напряжение ОУ. В суммирующей точке складываются два одинаковых тока: -Ubxi/R и С/вых/вхз ?. Для нормальной работы схемы эти токи должны иметь противоположную полярность. 32. Компараторы В схемах компараторов используются ОУ с разомкнутой ОС. На рис. 59, а приведена простейшая схема нуль-компаратора. Если, например, напряжение насыщения ОУ составляет ±10 В и К=*. = 10 000, то [/пор= 10/10 000=1 мВ. Подавая на вход схемы синусоидальный сигнал С/вх>20 мВ, на выходе получим практически прямоугольное переменное напряжение. Для ограничения выходного уровня в цепь ОС иногда включают стабилитроны или другие ограничители. Схема на рис. 59, в предназначена для сравнения разнополяр- ных напряжений. Входной сигнал 1/вх и опорное напряжение Ооп подаются на вход (-). При {/вх</оп /вых==-t/яао, при UBx>Von 1вых = -Ы/нас. В момент равенства 1/вх и t/on ОУ находится в неустойчивом линейном режиме. Переключение компаратора происходит с некоторой задержкой, которая определяется временем переза-

Рис. 59. Нуль-компаратор (а) и форма его выходного напряжения (б); компаратор разнополярных сигналов (в) и форма его выходного напряжения (г). ряда паразитных емкостей ОУ. Схема имеет низкое входное сопротивление, но позволяет сравнивать большие сигналы без появления смещения выходного напряжения от синфазной составляющей. Если сигнал и опорное напряжение подавать на разные входы ОУ, можно сравнивать сигналы одинаковой полярности. Сигналы t/вх и С/оп при Ьтом не должны превышать допустимого для данного ОУ синфазного напряжения. Часто возникает необходимость преобразовать аналоговые сигналы в цифровые. Для этих целей целесообразно применять интегральные компараторы, являющиеся специализированными ОУ. Обычные ОУ имеют большой размах выходного напряжения, что неприемлемо для управления логическими микросхемами. Выходное напряжение компаратора может находиться только на стандартных уровнях: логический О (-0,5-г--ь1,4 В) или логическая 1 (3-5 В). Компаратор считается сбалансированным, если его выходное напряжение находится в пределах 0,7-1,4 В (для ОУ выходное напряжение должно равняться нулю). За счет сокращения амплитудного диапазона быстродействие компаратора выше быстродействия стандартного ОУ, скорость отклика составляет около 50 не. На рис. 60, а показана основная схема использования компаратора типа 521СА2. На один из входов подается входной сигнал, (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) ( 12 ) (13) (14) (15) (16) (17) (18) (19) (20) |

|||||||||||||||||||||||

|

|