|

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) ( 12 ) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (12) д.еленности памяти, повышает надежность устройств за счет применения серийно освоенных БИС памяти, упрощает контроль функционирования устройства (контроль блока микропрограммного управления сводится, по существу, к контролю содержимого ЗУ). Передача управляющих слов в виде зашифрованных кодовых последовательностей соответствует условиям минимизации числа выводов БИС и снижению числа соединений в модулях. Регулярность структуры. Принцип регулярности предполагает закономерную повторяемость элементов структуры и связей между ними. Регулярность системы следует рас- сматривать на различных уровнях ее организации. Применение данного принципа позволяет повысить эффективность интегрального исполнения устройств вследствие увеличения интегральной плотности, уменьшения длин связей на кристалле, упрощения и сокращения времени топологического и схемотехнического проектирования БИС, упрощения процедур контроля топологии, уменьшения числа пересечений, сокращения числа типов функциональных и конструктивных элементов, повышения серийности и снижения стоимости средств. Основными путями увеличения регулярности структуры вычислительных и управляющих систем (ВУС) являются широкое использование структур и устройств типа памяти (ОЗУ, ПЗУ, ПЛМ), применение регистровых структур, отказ от закрепления определенных микроопераций за регистрами, выполнение регистров общего назначения в виде ячеек ОЗУ, использование магистрального способа обмена, стандартизация интерфейсов, использование принципа микропрограммного управления, вертикальное (поразрядное) разбиение структуры ЭВМ на БИС, развитие многопроцессорных параллельных систем. 3-2. АРХИТЕКТУРА ЭВМ Под архитектурой ЭВМ понимается абстрактное представление машины в терминах основных функциональных модулей, языка ЭВМ, структуры данных. Архитектура не определяет особенностей реализации аппаратной части ЭВМ, времени вьшолнения команд, степени параллелизма при выполнении программы, ширины шин и других аналогичных характеристик. Архитектура отображает аспекты структуры ЭВМ, которые являются видимыми для пользователя: систему команд, режимы адресации, форматы и длину данных, набор регистров ЭВМ, доступных пользователю. Одним словом, термин «архитектура» используется для описания возможностей, предоставляемых ЭВМ, а термин «организация» определяет, как эт.ч возможности реализованы. Все ЭВМ содержат следующие функциональные блоки, имеющие свою микроархитектуру: процессор, состоящий из арифметико-логического устройства и устройства управления, память, устройства ввода и устройства вывода информации (рис. 3-1). Объединение функциональных блоков в ЭВМ осуществляется посредством следующей системы ШИН; щины данных, по которой осуществляется обмен информацией между блоками ЭВМ, щины адреса, используемой для передачи адресов, по которым осуществляется обращение к различным устройствам ЭВМ, и щины управления для передачи управляющих сигналов. Для связи пользователя с ЭВМ предусмотрен пульт управления, который позволяет выполнять такие действия, как пуск ЭВМ; останов, под действием которого прекращается поступление сигналов с генератора тактирующих сиг- Процессор Адрес

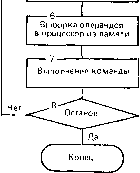

Ввод порта (данных Порт 1 Порт 2 ПортЗ Порт п УпрэБ-ление вводом Устройства ввода Регистр адреса памяти Шина данных Регистр данных иамнти Ячейка 1 Ячейка 2 Ячейка 3 Ячейка S Управление чтением, записью Память Управление выводом Шина адреса Вывод данных Устройства вывода Шина управле ния Адрес порта Порт 1 Порт, 2 ПортЗ Порт 171 Рис. 3-1. Структурная схема ЭВМ Рис. 3-2. Обобщенный алгоритм функционирования ЭВМ Начало Загрузка команды в регистр команд Формирование адреса следующей команды Дешифрация команды, формирование исполнительных адресов налов и процессор переходит в состояние ожидания; загрузка начального адреса программы в программный счетчик; индикация содержимого ячеек памяти и регистров процессора; пошаговое выполнение команд программы при ее отладке. Обобщенный алгоритм функционирования ЭВМ представлен на рис. 3-2. Одно из основных различий между ЭВМ - это организация системных шин, обеспечивающих связь между отдельными блоками ЭВМ; по этому признаку все структуры малых ЭВМ могут быть классифицированы следующим образом: ЭВМ с многошинной структурой; ЭВМ с общей шиной. Типичная архитектура ЭВМ с многошинной структурой представлена на рис. 3-3. Основная особенность ее организации состоит в том, что для каждого способа обмена информацией с периферийными устройствами используется отдельная группа шин: отдельные шины для программного режима обмена информацией с прерыванием или без прерывания выполняемой программы и для ввода-вывода информации в режиме прямого доступа периферийных устройств к памяти, которые передают блоки данных с большой скоростью (накопители на магнитных дисках, лентах, быстродействующие аналого-цифровые преобразователи и другие устройства). Протоколы обмена данными, структура шин и быстродействие при обмене для каждой из групп шин могут быть оптимальным образом адаптированы к обслуживаемым периферийным устройствам в соответствии с выбранным методом. Другой популярной структурой шин, которая использу-

(0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) ( 12 ) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

||||||||||||||||||||||

|

|