|

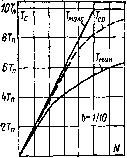

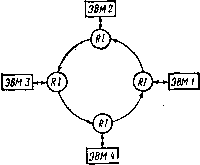

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) ( 121 ) (122) (123) (124) (121) Ь- 5 О 1 1 3 k 5 6 1  О 2 It 6 8 10 12 Hf Рис. 8-22. Зависимость общей производительности системы от числа процессоров иы, необходимых одному процессору. Его численное значение зависит от циклов команд процессоров и времени обращения памяти. Различают две структуры сильносвязанных систем: симметричную и асимметричную. В симметричной структуре все процессоры выполняют одну и ту же программу с различными данными. Когда в систему поступает запрос иа работу, управляющий элемент направляет его в любой свободный процессор. При отказе одного процессора нагрузка перераспределяется между другими процессорами. В асимметричной структуре каждый процессор выполняет различные задачи, а результаты используются другим процессором. Например, процессор ввода направляет данные в процессор с плавающей запятой, а тот передает результаты обработки в связной процессор. Таким образом, асимметричная структура характеризуется предопределенностью передач данных. Независимо от способа реализации системы (сильно- или слабосвя-заииая) необходимо установить иерархию между процессорными элементами. Элемент может быть ведущим (М-элемент) или ведомым (S-элемент). М-элемеит самостоятельно инициирует выполнение задачи и передачи данных. Каждый М-элемент (если их несколько) программируется с расчетом на его автономность в терминах данного алгоритма. Действия 8-элементов зависят от приказов М-элемеита о выполнении какой-либо задачи. Передачи результатов также могут осуществляться под управлением М-элемеита. M/S-системы довольно распространены, так как межпроцессорные связи проще реализовать, когда один М-элемент управляет несколькими S-элементами. М-элемент в M/S-системе иногда называют процессором распределения ресурсов, так как S-элементы начинают действия по приказам М-элемеита. Восьмибитные микропроцессоры с фиксированной системой команд и длиной слова практически ие имеют средств организации мультипроцессорных систем (схем последовательной связи и сигналов запроса шииы). Поэтому для реализации мультипроцессорной системы необходимы значительные дополнительные аппаратные средства. Рассмотрим некоторые вопросы объединения в сильносвязанную систему микропроцессоров КР580. Число объединяемых в систему микропроцессоров, обеспечивающее существенный прирост производительности, зависит в основном от чис- Состояние t CocmoMue2, Состояние N, Схема запросов записи и считывания Схема приорате та Схема управленш шиной памяти атм1 It dtm1 DFMN RDYN Рис. 8-23. Структура контроллера памяти ла периодов синхронизации в одном машинном цикле. В микропроцессоре КР580 каждая команда требует от 1 до 5 машинных циклов щ»-должительностью 3-5 периодов синхронизации. В первом машинном цикле из памяти всегда считывается код операции, а в зависимости от функции команды могут потребоваться дополнительные обращения к памяти. Статистический анализ большого числа программ показал, что одно обращение к памяти приходится на 3,5 периода синхронизации. Поэтому, если время обращения к памяти не более одного периода синхронизации, она может обслужить параллельно три микропроцессора. Однако неизбежно несколько меньшее увеличение производительности, чем трехкратное, так как при одновременном обращении к памяти нескольких микропроцессоров разрешается обращение одному из них, а остальные должны ожидать. Контроллер памяти, структура которого приведена на рис. 8-23, синхронизирует передачи данных между памятью и микропроцессорами. При наличии единственной шииы памяти обращения микропроцессоров к памяти должны подчиняться определенным правилам. Для каждого микропроцессора необходимы четыре управляющих сигнала, формируемых, когда микропроцессор выдает адрес иа шяиу адреса (мнемоника сигнала ATM - адрес в память), считывает данные с шины данных (мнемоника сигнала DFM - данные из памяти), выдает данные на шину данных (мнемоника сигнала DTM -данные в память) или когда необходимо приостановить обращение к шине, если память удовлетворяет запрос другого микропроцессора (мяемоиика сигнала RDY - готовность) . Указанные управляющие сигналы формируются из сигналов состояний микропроцессоров (SYNC, MEMR, WO и др.) с учетом приоритетов микропроцессоров. Наиболее просто реализуются фиксированные приоритеты. Отметим, что контроллер памяти должен иметь достаточно высокое быстродействие. Мультимашииные системы обрабатывают несколько входных потоков, в них нет единой операционной системы, а межмашинное взаимодействие осуществляется в основном на уровне данных. Однако в сложных ситуациях данные могут дополняться приказами на выполнение определенных действий. Одна из основных функций системы заключается в распределении различных задач для достижения максимальной производительности. В идеальном случае каждая ЭВМ системы выпожяет конкретную задачу я работает относительно независимо от других. Передачи данных между ЭВМ невелики по сравнению с общим потоком данных в системе. К настоящему времени разработано множество структур мультямашиниых систем, основные из которых рассматриваются ниже: •""  звм1] \ЭВМ2 ЭВМ 5 *-А с-элемент ЭВМ* Рис. 8-24. Кольцевая структура Рис. 8-25. Звездная структура Кольцевая структура. Система с кольцевой структурой опирается иа быстродействующую однонаправленную линию (канал) связи, которая образует замкнутый тракт -кольцо или петлю. ЭВМ и общие периферийные устройства подключаются к линии с помощью аппаратных устройств, называемых кольцевым интерфейсом RI (рис. 8-24). Взаимодействие между ЭВМ (узлами) системы осуществляется в виде сообщений, передаваемых по каналу. Сформированное узлом-передатчиком сообщение передается по каналу до тех пор, пока оно не~ достигнет адресованного узла-приемника или не возвратится в узел-передатчик. Сообщения из канала удаляет либо узел-передатчик, либо узел-приемиик. В первом случае узел-передатчик может сравнить исходное сообщение с сообщением, вернувшимся по каналу, и проконтролировать наличие ошибок. Узел-приемник сигнализирует о получении сообщения установкой определенного бита в этом сообщении. Во втором случае контроль ошибок выполняется узлом-приемником. Отметим, что во втором варианте нагрузка на канал связи уменьшается. Сообщения передаются с разделением во времени в виде адресуемых блоков, называемых пакетами илн кадрами. Локальный кольцевой интерфейс формирует кадр, вводит адрес узла-приемника и передает кадр в канал связи. Интерфейсы остальных узлов принимают кадр, проверяют адрес приемника и либо сразу ретранслируют кадр в канал (адреса приемника и интерфейса не совпали), либо удаляют кадр из канала и направляют сообщение подключенной ЭВМ (кадр достиг приемника). Кольцевая структура имеет следующие положительные качества: благодаря единственному каналу связи не возникает проблем маршрутизации сообщений; физическое размещение узла-приемника не играет роли, и упрощается передача сообщений для всех узлов; передачи по каналу осуществляются в цифровой форме с высокой скоростью, поэтому модемы и преобразователи данных не нужны. Основной недостаток кольцевой структуры - требование очень высокой надежности канала, так как отказ канала приводит к выходу из строя фактически всей системы. Для увеличения надежности системы применяется тот или иной способ дублирования канала связи. Звездная структура. В данной структуре одна ЭВМ образует центр (С-элемент), выполняющий в системе функции управления и соединен- (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) ( 121 ) (122) (123) (124) |

|

|