|

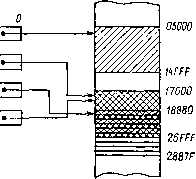

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) ( 21 ) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (21) Память 7 а Адре0 ш[ ss[ F.Sl 0500 1700 1700  Рис. 3-15. Адресация сегментов в МП 8086 Четыре 16-битных сегментных регистра CS, DS, SS и ES используются для задания текущих сегментов по 64К байт, адресуемых при выполнении программы (рис. 3-15). Каждый регистр адресует конкретный текущий сегмент, что отражено в их названиях: код, данные, стек, дополнительные данные. Сегментные регистры автоматически действуют в качестве базовых регистров при всех обращениях к памяти, т. е. исполнительный адрес суммируется с содержимым определенного сегментного регистра. Выборка всех команд осуществляется из текущего сегмента кода, а смещением служит содержимое указателя команд IP. Все исполнительные адреса данных (кроме адресов, формируемых через BP или SP, а в операциях с цепочками- через DI) суммируются с содержимым DS. Обращения к стеку, включая неявные действия при прерываниях, вызовах подпрограмм и возвратах, а также явные стековые включения и извлечения, осуществляются через SS. В операциях с цепочками и использованием DI физический адрес формируется через ES. Отметим, что любой команде с вычислением исполнительного адреса может предшествовать определяемый пользователем однобайтный префикс, в котором двухбитное поле явно определяет используемый сегмент. Основное назначение сегментных регистров - динамическое перемещение программ в памяти, которое необходимо в мультипрограммной среде. По существу, для такого перемещения достаточно модифицировать содержимое сегментного регистра CS при условии, что программа сама не изменяет его содержимого. Кроме того, модифицируя содержимое DS, прикладная программа может манипулировать данными такого объема, который превышает емкость сегмента. 16-битный регистр состояния (регистр флажков) FLAGS разделен на две половины, младшая из которых FLAGSL полностью соответствует регистру флажков микропроцессора 8080. В старшей половине введены 4 новых флажка: OF - арифметического переполнения; DF - направления (определяет направление сканирования массива в операциях с цепочками); IF - прерывания (выполняет функцию маскирования внешних прерываний); TF - прослеживания (обеспечивает выполнение программы по командам). Система команд микропроцессора 8086 не является подмножеством системы команд микропроцессора 8080. Хотя сохранена преемственность большинства команд, но некоторые редко используемые команды (например, условные вызовы и возвраты) исключены и введено много новых команд. Команды манипулируют одним или двумя операндами, а результат замещает один (часто любой) из операндов. Многие команды обрабатывают 8- и 16-битные операнды. Первым операндом в двухоперандной команде обычно является регистр или память, а во втором - регистр или константа (непосредственный операнд). В общем, нумерация операндов чисто условная и не отражает никакой направленности в передаче данных. Общий формат двухоперандной команды, когда вторым операндом является регистр, показан на рис. 3-16. Первый байт содержит код операции и два однобитных поля: d (направление) и w (слово). Поле d определяет направление передачи, относящееся ко второму операнду - регистру, идентифицируемому 3-битным полем reg второго байта команды. Если d = 1, то направление пе- reg- 31 diSpL I dispH I tj.- .----1 i---------- Рис. 3-16. Формат двухоперандной команды Разумеется, речь идет о содержимом регистра. 5* 67 редачи - в регистр, а если d = 0, то направление-из регистра. Поле W определяет тип операнда: слово (w = 1) или байт (w = 0). Второй байт команды, называемый постбайтом, имеет три поля. Поле reg определяет второй операнд, обязательно находящийся в регистре. В этом поле кодируются следующие 8- или 16-битные регистры: reg (г/т) . ООО 001 010 011 100 101 110 111 8 бит . . . AL CL DL BL АН СН DH ВН 16 бит. . . АХ СХ DX ВХ SP BP SI DI Поле режима mod определяет используемый режим адресации. В частности, оно влияет на интерпретацию содержимого поля r/m (регистр/память) при нахождении первого операнда. Поле mod имеет следующий общий смысл mod= I 00, 01, 10 - операнд содержится в памяти; 1 11 - операнд содержится в регистре. Когда mod = И, поле г/т определяет 8- или 16-битный регистр в соответствии с приведенным выше кодированием. Если moduli, это поле определяет, каким образом используется необязательное смещение disp: mod = 00, disp = о (байты disp L и disp Н отсутствуют); 01, disp=disp L (с расширением знака до 16 бит); 10, disp = disp Н, disp L (два байта смещения). В этом же случае (mod Ф 11) поле r/m определяет, как формируется исполнительный адрес ЕА команды:

Приведенные правила имеют только одно исключение; если mod = 00 и r/m = ПО, то ЕА = disp Н, disp L. Такой способ формирования ЕА называется прямой адресацией, т. е. адрес содержится в команде. Следовательно, операнд в памяти может адресоваться прямо (16-битное смещение) или косвенно (8- или 16-бит- (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) ( 21 ) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

|

|