|

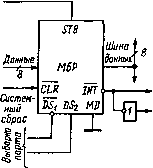

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) ( 41 ) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (41) STB-MB-XSi Шг JIh Sir Sis- Sh-ST.- CLR- J- и =[&]-SOi -SQi S , С INT -Sue -SOy -BOs Рис. 4-5. Многорежимный буферный регистр К589ИР12 регистра CLR=0, или при DSi-082 = 1 триггер прерывания устанавливается в 1. Рассмотрим некоторые примеры использования регистра К589ИР12 в микро-ЭВМ. Простейшее использование регистра - стробируемый буфер (рис. 4-6,а). Сигналы логической 1 (высокий потен-циал на входе STB и логического О (низкий потенциал) на входе MD обеспечивают постоянный прием данного в регистр. При DSiSD2=l содержимое регистра передается

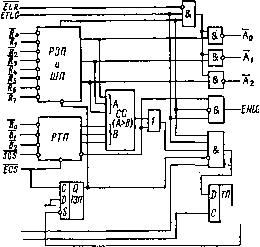

Вход строба Шина данных Шина  В БПП В процессор CLR BS, Щ MD Шина данных ЩЩ МЛ Шина данных Впроцес-сор Строб из периферийного устройства stb мбр т clr ЪЗ, ИЗг МВ Данные Системный сброс управления Рис. 4-6. Примеры использования МБР в интерфейсных схемах на выход (DOi-DOs), при DSi-082=0 выход регистра соответствует высокому сопротивлению. Два регистра К589ИР12 могут быть использованы для организации двунаправленного шинного формирователя (рис. 4-6,6). В данной схеме один из регистров работает в режиме стробируемого буфера, а другой находится в состоянии высокого сопротивления. Такой вариант целесообразно использовать в простых микро-ЭВМ. Использование регистра в качестве входного порта периферийного устройства приведено на рис. 4-6, е. При за- грузке данного в порт (STB = 1, MD=0) формируется сигнал прерывания INT, процессор идентифицирует порт и программа ввода обеспечивает передачу кода по шине данных в процессор при DSj-052=1. Регистр К589ИР12 может быть использован как выходной порт при передаче данных из процессора в периферийное устройство (рис. 4-6,г). Сигнал на входе STB выполняет функцию подтверждения получения данного периферийным устройством, и, кроме того, под действием этого сигнала вырабатывается сигнал прерывания INT в процессор для разрешения передачи следующего кода. Выборка порта обеспечивается сигналами на входах DSi и DS2. Блок приоритетных прерываний К589ИК14 (БПП) обеспечивает взаимодействие ЭВМ с внешней средой посредством обслуживания источников запросов в режиме прерывания (рис. 4-7). Рассмотрим вначале функциональное назначение выводов БПП: Ro-R7 - входь! запросов прерывания, низкий потенциал соответствует £ктивному запросу. Вход R7 имеет высший приоритет, а Ro - низший{ Во-Вг - входы для установки кода текущего приоритета! SGS - вход выборки группы, может использоваться для формирования сигнала прерывания из БПП только на ос-  CLK- Рис. 4-7. Блок приоритетных прерываний К589ИК14 (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) ( 41 ) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|