|

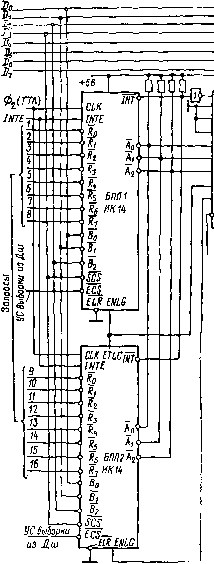

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) ( 43 ) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (43) шина ванных МП  int ъо stb ъо Si лз msp s3 si,ipl2si s5 ss se ss St d7 Ш-int (ВМП) reset ус выборки порта издш Рис. 4-9. Объединение БПП типа К589ИК14 Рис. 4-10. Шинный формирователь В Ог- & & & & -BBz & Аналогичным образом можно t t объединять большее число БПП -I-Ts для увеличения числа входов системы обработки прерываний. Необходимо заметить, что есть другие варианты объединения БПП, которые рассмотрены в литературе по проектированию микропроцессорных систем. Шинные формирователи К589АП16 и К589АП26. Для увеличения нагрузочной способности шин в микропроцессорные комплекты входят шинные Г1 & формирователи, которые могут - i-ВВ выполнять также дополнительные функции: осуществление электрической совместимости компонентов, отключение ис- g точников и приемников информации от шин, так как ЩЦ-обычно шинные формирователи gj-имеют три выходных состояния, обеспечение двунаправленного обмена информацией. Типичными представителями шинных формирователей являются 4-битные двунаправленные формирователи К589АП16 и К589АП26; причем последний имеет инверсные выходы. Структурная схема шинного формирователя К589АП16 приведена на рис. 4-10. Каждая линия шинного формирователя содержит две логические схемы И с тремя выходными состояниями. С одной стороны шинного формирователя входы и выходы схем И объединены (DBi-DB4), эти линии используются для интерфейса формирователя со схемами, совместимыми с ТТЛ. С другой стороны входы (DIi-DI4) и выходы (DOi-DO4) шинного формирователя являются раздельными с целью получения максимальной гибкости при использовании данной схемы. Они, конечно, могут быть соединены, например, при использовании шинного формирователя с двунаправленной шиной МП КР580. Вход CS управляет выборкой кристалла, при CS = 0 (низкий потенциал) формирователь выбирается и в зависимости от управляющего сигнала DIEN определяется направление передачи информации: при DIEN=1 содержимое ли- Шина daimix процессора g Шинный формироВатЕль Системная шина Ванных ЧпраЪление формирователе.- Регистр -состая-ния STSTB ВВШ WR HLDA Логическая схема -MEMR -MEMW llOR -now -BUSEN •mfh Рис. 4-11. Системный контроллер и шинный формирователь ний 01-DI4 передается на линии DB\-DB4, а при blEN = 0 имеет место передача с линией DBi-DB4 на линии DOi-DO4. Системный контроллер и шинный формирователь ВГ28 (СКШФ) предназначен для формирования системных управляющих сигналов (СУС), для непосредственного сопряжения МП КР580 с памятью и интерфейсными модулями периферийных устройств. Двунаправленный ШФ включен в БИС для увеличения нагрузочной способности шин данных МП. Структурная схема СКШФ приведена на рис. 4-11. В начале каждого машинного цикла микропроцессор по шине данных выдает код, определяющий тип машинного цикла, этот код по шине данных загружается в регистр состояния (РС) ВГ28 при поступлении сигнала STSTB из генератора тактовых сигналов. РС связан с логической схе-мой, которая формирует следующие управляющие сигналы. MEMR - сигнал чтения информации из памяти; MEMW - сигнал записи информации в память; I/QR - сигнал чтения информации из устройства ввода; I/OW - сигнал записи информации в устройство вывода; INTA -сигнал подтверждения прерывания. Входными сигналами в СКШФ являются: DBIN - сигнал приема информации в МП; WR -сигнал выдачи информа-циииз МП; HLDA - сигнал подтверждения захвата МП; BUSEN -сигнал, соответствующий 1, который переводит шину данных и линии управляющих сигналов в состояние высокого сопротивления для отключения МП от системных шин при организации обмена в режиме прямого доступа к памяти. (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) ( 43 ) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

|

|