|

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) ( 44 ) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (44) 4-4. ПРОГРАММИРУЕМЫЙ АДАПТЕР ПОСЛЕДОЗАТЕЛЬНОГО ИНТЕРФЕЙСА В некоторых применениях мини- и микро-ЭВМ необходимо осуществлять обмен данными в последовательном формате. Такой обмен характерен для интерфейсов медленнодействующих или удаленных периферийных устройств, а также для интерфейсов распределенных систем обработки. В большинстве микропроцессорных семейств имеются программируемые БИС, предназначенные для интерфейса параллельного процессора с последовательным периферийным оборудованием. Эти БИС называются универсальными приемопередатчиками, программируемым связным интерфейсом нли адаптерами последовательной связи. Единицей обмена в последовательном формате является символ, представленный водной из систем кодирования и содержащий 5-8 бит. Примером 5-битного кода служит международный телеграфный код № 2. Биты кодируются наличием тока в линии (1 или MARK) либо отсутствием тока (О или SPACE). На практике применяются два режима последовательного обмена: асинхронный (старт-стопный) и синхронный. В первом из них каждый символ передается автономно и передача может быть начата в любой момент времени. Стандартный формат символа в асинхронной связи приведен на рис. 4-12, а. Передача начинается со стартового бита, т. е. прекращения тока в линии связи. Затем в зависимости от применяемого кода передаются 5-8 бит собственно символа. Передача символа завершается необязательным битом четного или нечетного паритета и одним, полутора или двумя стоповыми битами. После этого может быть начат цикл передачи следующего символа. Скорость пере- а) Ст<уп Код сипвола Пщштт Стоп

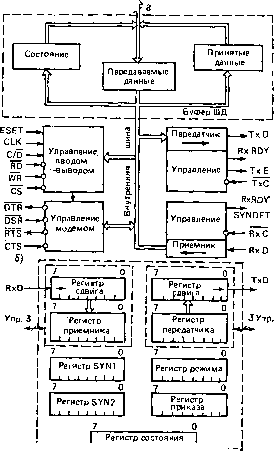

Рис. 4-12. Формат асинхронной передачи (а), формат синхронной передачи (б) дачи измеряется либо числом символов в секунду (l/T)", либо числом битовых посылок в секунду (1/т). Синхронная передача начинается с одного или двух специальных символов синхронизации SYN1 и SYN2, после которых последовательно без всяких разделителей передаются 5-8-битные коды символов с необязательными битами четного или нечетного паритета (рис. 4-12,6). В обоих режимах необходимо контролировать передачу по битам паритета (если они предусмотрены в формате), выдерживать необходимые временные соотношения, а в асинхронном режиме дополнительно контролировать установленный формат (кадр) символа. Из рис. 4-12, а видно, что асинхронному режиму свойственна значительная избыточность. Если, например, код символа содержит 5 бит, то вместе с ним могут передаваться до 4 служебных бит. Непроизводительное использование линии связи доходит до 44 %, поэтому асинхронный режим применяется в системах с небольшой скоростью передачи или с нерегулярным обменом. Некоторые БИС последовательного интерфейса могут работать только в синхронном (универсальные синхронные приемопередатчики - УСПП) или в асинхронном (универсальные асинхронные приемопередатчики -УАПП) режиме. Наибольшей же гибкостью отличаются БИС универсальных синхронно-асинхронных приемопередатчиков (УСАПП), которые допускают программирование любого режима работы. Типичным примером УСАПП является микросхема КР580ВВ51, реализующая практически любой способ последовательной связи. Далее ради краткости она называется адаптером последовательного интерфейса или просто адаптером. Адаптер должен автоматически производить параллельно-последовательные (при передаче) и последовательно-параллельные (при приеме) преобразования, а длят процессора выглядеть устройством параллельного ввода и вывода. Он может работать в полудуплексном или дуплексном режимах, обеспечивающих одновременную одностороннюю или двухстороннюю связь. Наличие в схеме двойных буферов приводит к тому, что для реакции на запрос прерывания адаптера в распоряжении процессора имеется временной интервал Т передачи одного символа. Адаптер также генерирует и воспринимает сигналы управления модемом. На рис. 4-13 приведены структурная схема и программная модель адаптера, а на рис. 4-14 подключение его к системной шине. Рассмотрим основные компоненты адаптера.

Модем Рис. 4-13. Структурная схема (а) и программная модель (б) микросхемы КР580ВВ51 Параллельный 8-битный двунаправленный буфер шины данных D7-0 с тристабильными каскадами служит для передачи собственно данных, управляющих слов и информации состояния. Обычно обмен инициируется командами ввода IN и вывода OUT. Схема управления воспринимает сигналы с шины управления и генерирует внутренние управляющие сигналы. В ее (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) ( 44 ) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

||||||||||||||||||||

|

|