|

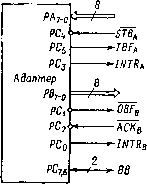

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) ( 49 ) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (49) Здесь CWR - символический адрес регистра управления, который определяется интерфейсом адаптера с системной шиной. Например, им может быть CWR = 0F7H. Отметим, что в приведенном фрагменте можно сэкономить один байт, заменив вторую команду MVI на команду DCR А. Аналогичная функция установки и сброса отдельных бит портов А и В реализуется в три этапа: содержимое порта вводится в аккумулятор, командами ORI и ANI с соответствующими операндами-масками модифицируется нужный бит, а затем измененный результат выводится в тот же порт. Как видно из приказа определения режима, адаптер имеет три режима работы. Рассмотрим некоторые особенности каждого из режимов. В режиме О базового ввода-вывода могут работать все три порта, причем порт С разделяется на два независимых 4-битных порта. Всего, таким образом, получается два 8-битных и два 4-битных порта параллельного ввода или вывода, что обеспечивает 16 возможных конфигураций адаптера в режиме 0. Выводимые данные фиксируются в регистрах-защелках, входящих в состав всех портов, а вводимые данные не запоминаются, т. е. в операции считывания входного порта в аккумулятор передается текущее состояние входных линий. Режим О применяется в программно-управляемом вводе-выводе с медленнодействующими периферийными уст- Адаптер РС, РС, PCk РСо РСз РС, READY READY REAHY Посикёвтньш принтер fleptpopomcp Считыватель \ He используются Рис. 4-18. Интерфейс адаптера с принтером и перфоратором-считывателем ройствами. На рис. 4-18 приведен интерфейс адаптера с посимвольным принтером и ленточным перфоратором-считывателем. Два устройства вывода (принтер и перфоратор) разделяют общую шину данных порта А. Будем считать, что состояние готовности всех устройств представлено Н-активными сигналами READY и собственно передача данных сопровождается L-активными стробирующими сигналами STB. Приказ режима должен определить следующую конфигурацию адаптера: порт А -вывод, порт В - ввод, порт С РСз-о-ввод, порт С РС7 4-вывод. Данную конфигурацию определяет приказ 10000011 (83Н). Ради простоты воспользуемся символическими адресами регистров адаптера: PORT А -порт А, PORT В -порт В, PORT С - порт С н CWR -регистр управления. Действительные значения этих адресов зависят от подключения адаптера к системной шине адреса и должны быть определены в программе. Для организации ввода-вывода необходима подпрограмма инициализации адаптера и три аналогичные подпрограммы ввода и вывода для каждого периферийного устройства. Каждая из них выполняет следующие действия: ввод состояния устройства, проверку готовности, вывод или ввод данных и формирование сопровождающего строба. Если устройство не готово к обмену, микропроцессор входит в цикл ожидания. Режим 1 стробируемого ввода-вывода предназначен для однонаправленных передач данных инициируемых прерываниями. Собственно передача слов данных осуществляется через порты А и В, а шесть линий порта С используются для управления обменом. Данный режим предоставляет пользователю следующие возможности: запрограммировать один или два параллельных порта с линиями квитирования и прерывания, каждый из которых может работать на ввод или вывод; при использовании только одного порта остальные 13 линий запрограммировать в режиме 0; при определении двух портов в режим 1 оставшиеся 2 линии использовать для ввода или вывода. На рис. 4-19 показана одна из возможных конфигураций адаптера, в которой оба порта А и В работают в режиме 1. Приказ определения этой конфигурации имеет вид lOIlDslOX, где Ds задает использование линий PCej для ввода (1) или вывода (0). Для операции ввода определяются следующие управляющие сигналы: STB (строб ввода) - импульсный входной сигнал от

Вывод Рис. 4-19. Конфигурация Рис.4-20. Форматы слов состояния режи-адаптера в режиме 1 ма 1 (ввод и вывод) устройства ввода, загружает данные, вводимые во входной регистр-защелку. IBF (входной буфер загружен) - выходной сигнал подтверждения восприятия данных; устанавливается спадом STB и сбрасывается фронтом RD. INTR (запрос прерывания) - входной сигнал прерывания микропроцессора; устанавливается при следующих условиях: STB=1, IBF=1, INTE = 1; сбрасывается спадом сигнала RD. Сигналом ШТЕ разрещения прерываний порта А можно управлять с помощью установки и сброса бита рс4, а порта В - с помощью установки и сброса бита РСг- Операцию вывода характеризуют также три сигнала: OBF (выходной буфер загружен) - входной сигнал в устройство вывода о наличии данных в порту; формируется после заверщения фронта WR и оканчивается L-уров-нем АСК. АСК (подтверждение) - входной сигнал от периферийного устройства, подтверждающий восприятие данных из адаптера. INTR (запрос прерывания) - выходной сигнал прерывания микропроцессора; устанавливается при выполнении условий АСК = 1, 0BF=1, INTE = 1 и сбрасывается спадом WR, когда микропроцессор записывает в адаптер новые данные. (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) ( 49 ) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

|

|