|

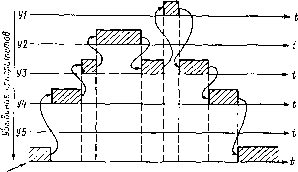

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) ( 59 ) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (59)  Основная * * * программа Рис. 5-9. Вложение прерываний каким-либо образом очень быстро (ц, пределе с быстродействием комбинационных схем) идентифицировать запрос прерывания устройства с максимальным приоритетом из имеющихся запросов прерываний; фиксировать текущий приоритет (порог) любой выполняемой процессором программы (в том числе и всех подпрограмм обслуживания прерываний) и разрешать ее прерывание только при возникновении запроса прерывания с большим приоритетом. Прерывание подпрограмм обслуживания прерываний называется вложением прерываний (рис. 5-9). До момента ti выполняется основная программа, которой назначается наименьший приоритет, чтобы процессор реагировал на любые прерывания. В момент ti запрашиёает обслуживания устройство У4 и процессор переходит на его подпрограмму обслуживания. В свою очередь, эта подпрограмма прерывается в момент t2 запросом от устройства УЗ с более высоким приоритетом. Подпрограмма обслуживания УЗ в момент ts прерывается запросом устройства У2 с еще более высоким приоритетом, и по завершении обслуживания У2 в момент t4 управление возвращается к продолжению обслуживания устройства УЗ. В интервале ts - te аналогичным образом обслуживается запрос устройства У1 с максимальным приоритетом, после чего управление последовательно возвращается к прерванным подпрограммам обслуживания устройства УЗ и У4. Наконец, в момент tg возобновляется выполнение основной программы. Разумеется, чтобы про- цессор реагировал на запросы прерываний, в начале каждой подпрограммы обслуживания их необходимо разрешать командой EI. В микро-ЭВМ указанные выше проблемы обычно решаются с помощью специальных БИС приоритетных прерываний, типичным примером которых является микросхема К589ИК14. Она рассчитана на подключение сигналов запросов прерываний восьми периферийных устройств, но допускает простое увеличение числа запросов до 64, для чего потребуется 9 таких микросхем без дополнительных элементов. Запросы устройств фиксируются в регистре-защелке, а подключенный к не>1у шифратор приоритетов формирует 3-битный код запроса с максимальным приоритетом из имеющихся запросов. Этот код при помощи комбинационного компаратора сравнивается с содержимым 3-битного регистра текущего приоритета. Этот регистр также входит в состав микросхемы и допускает программную загрузку. Схема фЬрмирует сигнал прерывания INT в микропроцессор, если среди имеющихся запросов прерываний присутствует запрос, приоритет которого выше текущего приоритета. По сигналу подтверждения прерывания INTA на выходе схемы появляется 3-битный код XXX приоритета запроса, на который должен реагировать микропроцессор. Этот код с помощью регистра К589ИР12 трансформируется в однобайтную команду повторного старта RST, имеющую код операции 11XXXI11. Когда микропроцессор КР 580 в конце текущей команды воспринимает запрос прерывания, он сбрасывает внутренний триггер INTE разрешения прерываний и вводит особый машинный Щ1КЛ прерывания, напоминающий цикл Ml выборки кода операции следующей команды. В такте Tl на шину адреса выдается содержимое программного счетчика, а на шину данных - байт состояния, в котором бит MEMR считывания из памяти сброшен, а бит INTA подтверждения прерывания установлен. В такте Tj запрещается инкремент программного счетчика и в счетчике сохраняется адрес команды, которая выполнялась бы при отсутствии прерывания (адрес возврата). Посредством объединения по схеме И сигнала DBIN приема с шины данных и бита состояния INTA фюрмирует-ся импульсный сигнал INTA. Этот сигнал через схему приоритетных прерываний выдает на шину данных код ПХХХ111. а микропроцессор загружает его в регистр команды. Таким образом, в данном цикле схема приори- тетных прерываний как бы заменяет программную память. Команда рестарта RST инициирует выполнение двух действий, аналогичных действиям команды CALL вызова подпрограммы: текущее содержимое программного счетчика включается в стек, для чего вводятся два цикла М2 и МЗ записи в стек; в программный счетчик загружается адрес ячейки повторного старта ООООООООООХХХООО, причем биты XXX берутся из регистра команды. Таким образом, в программном счетчике оказывается один из восьми адресов 0000, 0008,..., 0038, определяемый кодом XXX, который, в свою очередь, зависит от устройства, вызвавшего прерывание программы. Указанные адреса являются начальными адресами восьми подпрограмм обслуживания прерываний. На каждую подпрограмму резервируется всего 8 байт, но с помощью безусловного перехода она может быть продолжена в любой области памяти. Реакция микропроцессора (выполнение команды RSTJ длится 11 тактов синхронизации или 5,5 мкс при частоте синхронизации 2 МГц. Для организации вложенных прерываний в каждой подпрограмме обслуживания прерываний необходимо выполнить следующие действия: разрешить прерывания; временно запомнить приоритет прерываемой программы; загрузить в схему приоритетных прерываний новый текущий приоритет; собственно обслужить прерывание, т. е. выполнить передачу данных; восстановить прежний приоритет; возобновить прерванную программу с помощью команды возврата RET. Двумерные многоуровневые векторные прерывания. В мини-ЭВМ старших моделей, например в процессорах СМ, для которых характерно значительное число периферийных устройств с различным быстродействием, реализуется более сложная, но и более гибкая система прерываний. Она рассчитана на обработку не только внешних аппаратных прерываний от периферийных устройств, но и внутренних аппаратных прерываний, инициируемых при выполнении программы в случае возникновения особых ситуаций (переполнение, нереализованная операция и др.). Система прерываний называется многоуровневой, если процессор имеет несколько линий (уровней) запросов прерываний и если подпрограммы обслуживания одного уровня могут прерываться запросами на другом уровне. При наличии п уровней допустимая глубина вложений преры- (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) ( 59 ) (60) (61) (62) (63) (64) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

|

|