|

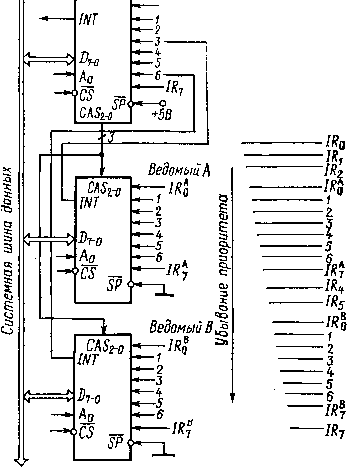

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) ( 64 ) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (64) разрешенными и после окончания фрагмента, в котором они допустимы. Для временного прекращения действия бита ISR служит приказ установки режима SMM. Когда задан этот режим, он действует до его сброса специальным приказом. Действие данного режима иллюстрирует следующая схема подпрограммы обслуживания прерывания от входа IR4. Как и в предыдущем примере, символические адреса ADR1 и ADR2 обеспечивают выбор контроллера (CS=0) и имеют, соответственно, нулевое и единичное значения младшего бита, а линия Ао шины адреса подключена на вход Ао контроллера: Метка Код Операнд Комментарий IR4: EI ; Разрешение прерываний про- ; цессора ; Здесь фрагмент, где прерывания с меньшими приоритетами ; запрещены D1 ; Запрещение прерываний на ; приказы MVI А, ЮН ; Маскирование входа IR4 OUT ADR2 MVI А, 68Н ; Установка режима специаль- ; ной маски OUT ADR1 ; Разрешение прерываний про- Е1 ; цессора Здесь фрагмент, где прерывания с меньшими приоритетами разрешены DI ; Запрещение прерываний на ; приказы MVI А, 48Н ; Сброс режима специальной OUT ADR1 ; маски MVI А, ООН ; Сброс маски на входе IR4 OUT ADR2 EI ; Разрешение прерываний про- ; цессора Здесь фрагмент, где прерывания с меньшими приоритетами запрещены. Должен заканчиваться соответствующим приказом EOI RET ; Возврат Установка режима специальной маски относится ко всем замаскированным входам. Если, например, в приведенной подпрограмме возникает запрос IRi, когда установлен режим специальной маски, а затем подпрограмма маскирует его, то запросы IR2 и IR3 с меньшими приоритетами будут разрешены. Следующий приказ OCW3 относится к режиму опроса, в котором для идентификации периферийного устройства, запращивающего обслуживания, процессор опрашивает не сами устройства, а контроллер, который может работать в любом режиме. Приказ опроса с установленным битом Р (D2=l) выдается в контроллер командой OUT. Следующий импульс RD, генерируемый при выполнении команды IN, выдает на щину данных слово состояний прерываний. В этом слове старший бит D7 (I)- фиксирует наличие прерывания, биты De-a не используются, а биты D2-0 (поле W2-0) идентифицируют код имеющегося запроса прерывания с наибольшим приоритетом. Обслуживание запросов устройств осуществляется программной дешифрацией считанного слова и переходом к соответствующей подпрограмме. Перед считыванием всегда необходимо загрузить приказ OCW3. В том случае когда прерывания отсутствуют, считанное слово содержит 1=0 и W2-o=lll. Режим опроса может оказаться удобным в системах с большим числом контроллеров, каждый из которых должен быть правильно инициализирован (начальные адреса в приказах ICW могут быть фиктивными) . Последняя функция OCW3 -считывание состояния контроллера, представленного содержимым регистров IRR, ISR и IMR. Регистры считываются при загрузке соответствующего приказа OCW3 с последующим выполнением команды IN или подаче импульса RD. Не требуется записывать OCW3 перед каждым считыванием состояния, если считывается тот же регистр, что и в предыдущей операции. Для считывания содержимого регистра IMR не нужен приказ OCW3, так как на линиях данных Dy-o контроллера находится это содержимое, если RD=Oh Ао=1. Каскадное включение контроллеров. Схема контроллера обеспечивает простое увеличение числа запросов прерываний до 64. На рис. 5-15 показана конфигурация с одним ведущим и двумя ведомыми контроллерами, имеющая 22 входа запросов прерываний. Ведущий контроллер определяется высоким уровнем сигнала на входе SP, а у ведомых приборов этот вход заземлен. Выходы INT ведомых контроллеров подключаются ко входам IR ведущего контроллера. Все линии CAS2-0 соединяются параллельно и являются выходными у ведущего и входными у ведомых контроллеров. Сигналами на этих линиях ведущий контроллер вы- цессор Ведущий  Рис. 5-15. Сопряжение трех контроллеров прерывании бирает соответствующий ведомый контроллер, который передает в процессор адрес подпрограммы. Когда на входе IR ведомого прибора появляется сигнал запроса прерывания, приоритет которого выше обслуживаемого им прерывания, на выходе INT формируется высокий уровень. С учетом приоритета прерывания, обслуживаемого ведущим контроллером, на его выходе INT появляется сигнал прерывания процессора. В ответ на первый им- (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) ( 64 ) (65) (66) (67) (68) (69) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

|

|