|

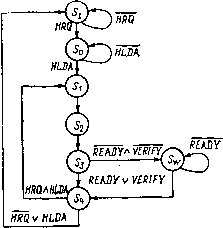

| Главная -> Книги (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) ( 69 ) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) (69) ходных данных, чтобы случайные запросы ПДП не исказили содержимого основной памяти. Четыре младших бита ЕЫз о определяют состояние соответствующих каналов ПДП. Если ENi = 0, т.е. 1-й канал запрещен, контроллер не реагирует на запрос DRQi; когда же ENi=l, т.е. 1-й канал разрешен, контроллер удовлетворяет запрос DRQi. Бит RP определяет фиксированный приоритет запросов ПДП (RP==0) или циклический приоритет (RP=1). При установке бита EW расширенной (удлиненной) за-писи несколько увеличивается продолжительность сигналов MEMW и I/OW, генерируемых контроллером. Это позволяет не вводить дополнительного состояния ожидания через сигнал готовности READY и несколько увеличивает скорость передачи данных. Если установлен бит TCS разрешения останова при окончании передач ПДП, после формирования сигнала ТС соответствующий канал ПДП запрещается, т. е. его бит EN сбрасывается. Дальнейшие передачи в этом канале возможны только после повторной загрузки регистра режима контроллера. Когда же TCS = 0, появление сигнала ТС не влияет на состояние канала ПДП и закончить операции ПДП должно периферийное устройство. Бит AL автозагрузки позволяет использовать канал Кг для повторных передач предыдущего блока данных или сцепленных блоков данных без программного вмешательства между передачами блоков. Для этого регистры К2 инициализируются обычным образом, а в регистры Кз загружаются параметры повторной инициализации Кг- После завершения в Кг передачи первого блока данных, о чем сигнализирует ТС = 1, в цикле модификации (обновления) параметры из регистров Кз загружаются в регистры Кг-При этом состояние бита TCS (если AL=1) не влияет на работу Кг- Когда AL=1, при программировании Кг его начальные параметры автоматически дублируются в регистрах Кз, что обеспечивает повторяющиеся передачи одного и того же блока данных. Такое повторение удобно при использовании КПДП для регенерации видеодисплея. Но в регистры Кз после загрузки регистров Кг допускается загружать другие значения параметров. Восьмибитный регистр состояния содержит четыре бита ТС, отражающих состояния окончания счета соответствующих каналов ПДП, и бит UF флажка модификации. Биты ТС устанавливаются одновременно с выдачей сигнала ТС соответствующих каналов и сбрасываются сигналом RESET или при считывании содержимого регистра состояния в процессор. Флажок UF устанавливается, когда в режиме автозагрузки параметры Кз передаются в регистры Кг, и не сбрасывается при считывании состояния. Его можно перевести в нулевое состояние посредством сигнала RESET или аннулирования режима автозагрузки. Кроме того, флажок автоматически сбрасывается после передачи первого блока вслед за модификацией регистров Кг- Контролируя состояние UF, процессор определяет момент завершения повторной инициализации Кг и, следовательно, возможность безопасной загрузки параметров нового блока данных. Программирование КПДП осуществляется командами OUT или любыми командами запоминания байта при использовании ввода-вывода, отображенного на память. При этом сигналы на линиях Аз о определяют адрес целевого внутреннего регистра, а сигналы на линиях Ai5 4 после дешифрации используются для формирования сигнала CS. Собственно запись в целевой регистр выполняется сигналом I/OW. Выбор регистров контроллера определяется табл. 5-5. Таблица 5-5 Адресация внутренних регистров контроллера Регистр Байт Линии адреса Линии шины даннык Адрес Ко Счетчик Ко Адрес Ki Счетчик Ki Адрес Ка Счетчик Кг Адрес Кз Счетчик Кз Режим Состояние Младший Старший Младший Старший Младший Старший Младший Старший Младший Старший Младший Старший Младший Старший Младший Старший С, Чт Аю Сю Аналогично Ко AL О TCS О EW О RP UF ENs ТСз ENjENi TCilTCi RESET  Рис. 5-21. Диаграмма состояний контроллера Бит Аз определяет обращение к канальным регистрам (Аз = 0) или к регистрам режима и состояния (Аз=1). При выборе канального регистра бит Ао идентифицирует регистр адреса (Ао = 0) или счетчик (Ао = 1). Оставщиеся входные линии адреса Аг,! определяют один из четырех каналов. Для загрузки и считывания содержимого каждого из 16-битных регистров необходимы две команды. В контроллере предусмотрен специальный триггер F/L (первый/второй, или младщий/старщий), состояние которого определяет старщую или младщую половину выбранного канального регистра. Триггер F/L сбрасывается при действии сигнала RESET и при загрузке регистра режима КПДП. Для обеспечения правильной инициализации команды обращения к канальным регистрам должны быть парными и первая из них должна обращаться к младшей половине регистра. Нельзя формировать CS = 0 при активном уровне сигналов I/OW или I/OR, так как это вызовет ошибочный переход триггера F/L. В системе с возможными прерыва-нияки при программировании КПДП или считывании содержимого его регистров прерывания следует запрещать. Контроллер имеет семь внутренних состояний, связи между которыми показаны на рис. 5-21. В холостом состоянии Si он не выполняет операций ПДП. Цикл ПДП начи- (0) (1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22) (23) (24) (25) (26) (27) (28) (29) (30) (31) (32) (33) (34) (35) (36) (37) (38) (39) (40) (41) (42) (43) (44) (45) (46) (47) (48) (49) (50) (51) (52) (53) (54) (55) (56) (57) (58) (59) (60) (61) (62) (63) (64) (65) (66) (67) (68) ( 69 ) (70) (71) (72) (73) (74) (75) (76) (77) (78) (79) (80) (81) (82) (83) (84) (85) (86) (87) (88) (89) (90) (91) (92) (93) (94) (95) (96) (97) (98) (99) (100) (101) (102) (103) (104) (105) (106) (107) (108) (109) (110) (111) (112) (113) (114) (115) (116) (117) (118) (119) (120) (121) (122) (123) (124) |

|

|